|

DOI: 10.7256/2453-8884.2018.4.28130

Дата направления статьи в редакцию:

25-11-2018

Дата публикации:

02-02-2019

Аннотация:

В связи с малым потреблением мощности КМОП структуры являются предпочтительными для создания больших и сверхбольших интегральных схем. Однако надежность схем в значительной степени ограничивается возникающим в КМОП структурах явлением защелки. Электрическая характеристика явления защелки в КМОП интегральных схема характерна наличием ряда аномальных явлений. Эти эффекты искажают и делают неоднозначными результаты измерения электрической чувствительности схем к защелке. Развитие микроэлектроники неуклонно стремится к уменьшению размеров элементов интегральных схем, в частности транзисторов. Уменьшение размеров интегральных схем, приводит к усилению короткоканальных эффектов в МОП- транзисторах. При уменьшении размеров интегральных элементов рассматриваются различные варианты масштабирования приборов со структурой металл-оксид-полупроводник. В качестве методов предотвращения защелкивания предлагаются использование диодов с барьером Шоттки или специальных поликремниевых диодов вместо омических контактов подложки и кармана; применение сильнолегированной подложки с изоляцией глубокими канавками. Механизмы, вызывающие появления защелкивания, не зависит от типа проводимости полупроводниковой области кармана.

Ключевые слова:

транзистор, защелкивание, МОП, масштабирование, СБИС, короткоканальные эффекты, полупроводник, наноэлектроника, отказ, моделирование

Abstract: Due to the low power consumption, CMOS structures are preferred for creating large and ultra-large integrated circuits. However, the reliability of the circuits is largely limited by the latch phenomenon that occurs in CMOS structures. The electrical characteristic of the latch up phenomenon in a CMOS integrated circuit is characterized by the presence of a number of anomalous phenomena. These effects distort and make ambiguous the results of measuring the electrical sensitivity of the circuits to the latch. The development of microelectronics is constantly striving to reduce the size of the elements of integrated circuits, in particular transistors. Reducing the size of integrated circuits leads to the amplification of short-channel effects in MOS transistors. When reducing the size of integral elements, various options for scaling devices with a metal-oxide-semiconductor structure are considered. The mechanisms that cause the appearance of the snap-in do not depend on the conductivity type of the semiconductor region of the pocket.

Keywords: transistor, latch up, MOS, scaling, VLSI, short channel effects, semiconductor, nanoelectronic, failure, modeling

В связи с малым потреблением мощности КМОП структуры являются предпочтительными для создания больших и сверхбольших интегральных схем [1-2]. Однако надежность схем в значительной степени ограничивается возникающим в КМОП структурах явлением защелки [3-6]. Электрическая характеристика явления защелки в КМОП интегральных схема характерна наличием ряда аномальных явлений [7]:

1. гистерезисом вольтамперных характеристик, снимаемых при постоянном напряжении и токе;

2. вариацией установившихся токовых характеристик защелки из-за увеличения пульсирующего тока, инжектируемого входными/выходными выводами;

3. наличием для значений напряжения питания определенных интервалов пульсирующего инжектируемого тока с нижним и верхним пределом, обеспечивающим защелки.

Эти эффекты искажают и делают неоднозначными результаты измерения электрической чувствительности схем к защелке.

Защелка, ведущая к практическому отказу интегральных схем, часто начинается с инжекции тока в подложки или в карман. Этот ток, в связи с падением напряжения в подложке или в кармане, ведет к смещению р-n перехода. При этом очень важно, каково сопротивление обоих областей и при большом сопротивлении, вероятность перехода схемы на работу в режим защелки повышается.

Развитие микроэлектроники неуклонно стремится к уменьшению размеров элементов интегральных схем, в частности транзисторов. Уменьшение размеров интегральных схем, приводит к усилению короткоканальных эффектов в МОП- транзисторах. При уменьшении размеров интегральных элементов рассматриваются различные варианты масштабирования МОП приборов. Среди них можно выделить три основных [8]:

1. концепция постоянного поля, когда напряжение и ток питания уменьшаются в n- раз;

2. концепция постоянного напряжения связана с решением проблемы генерации горячих дырок, что особенно существенно для СБИС;

3. пропорциональное уменьшение размеров, он является компромиссным по отношению к двум предыдущим.

Уменьшение размеров элементов интегральных схем, ведет к развитию короткоканальных эффектов в МОП- транзисторах. Один из этих эффектов это - умножение стокового тока. В зависимости от шунтирующего сопротивления этот ток может вызывать появление защелки, создавая смешение истокового перехода. Защелка возникает, если паразитный вертикальный биполярный транзистор смещен током, протекающим через паразитный резистор. В зависимости от длины затвора и от величины сопротивления определяется максимально допустимое рабочее напряжение, при котором еще не возникает защелка.

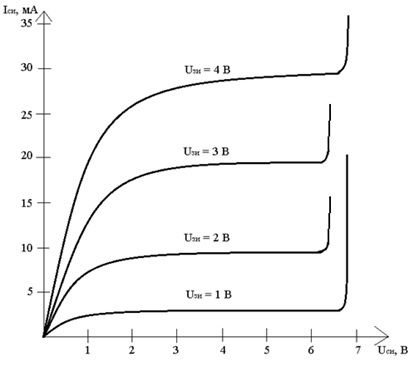

Если транзистор находится в режиме насыщения, большие напряженности поля на стоковом переходе вызывают генерацию электронно-дырочных пар. Большая часть генерируемых электронов течет к стоковому переходу, генерируемые дырки перемещаются к истоку. При оценке распределения потенциалов по поверхности площадь между истоком и стоком может быть распределена на две части. В первой, которая расположена поблизости от истока, может быть принято постепенное нарастание. Во второй части, в истощения между истоком и стоком, и воздействие продольного электрического поля становится более существенным, чем воздействие вертикального электрического поля. Ток умножения присутствует в МОП- транзисторах, которые работают в режиме насыщения. Этот ток может, без воздействия дополнительных "срывающих" в защелку факторов, вызвать переход схемы в режим работы вызывающем отказ схемы. Это видно из зависимости (рис. 1) тока сток-исток от напряжения сток-исток, для различных значений напряжения затвор- исток. Для исследуемых структур и средних значений сигнала, 2- 3 В, защелка возникает при напряжениях сток-исток порядка 6.3 В, т.е. задолго до достижения напряжения пробоя перехода, которое имеет порядок 10 В. Напряжение в 6.3 В является максимально допустимым рабочим напряжением для этого транзистора, при более высоких напряжениях возникает защелка.

Рис. 1. Зависимость тока сток-исток от напряжения сток-исток, для различных значений напряжения затвор-исток.

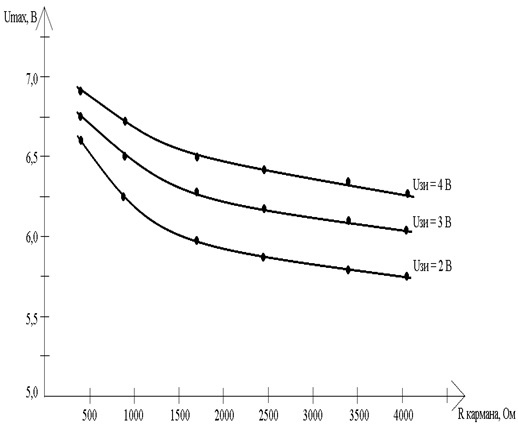

Сопротивление кармана имеет особенно большое значение для характеристик приборов, так как сопротивление влияет на смещение вертикального паразитного n-р-n транзистора. Сопротивление зависит от конфигурации. Суммарное сопротивление кармана может быть подсчитано как сумма сопротивлений участков.

На рис. 2 показана зависимость максимально допустимого рабочего напряжения от величины сопротивления кармана при разных рабочих напряжениях.

Уменьшение длины затвора при постоянном сопротивлении кармана снижает допустимое по условиям возникновения защелки максимальное рабочее напряжение.

Уменьшение размеров элементов снижает потребление схем, понижает задержки, а значит, повышает быстродействие схем, увеличивает функциональные возможности схем. Уменьшение размеров транзисторов влечет за собой изменение других параметров и характеристик, в частности, сопротивления кармана, формы перехода и др. Все это неминуемо влечет за собой изменение критических значений напряжений питания, при которых возникает защелка. Все эти влияния были оценены моделированием и экспериментами.

Рис. 2. Зависимость максимально допустимого рабочего напряжения от величины сопротивления кармана при разных рабочих напряжениях затвор-исток.

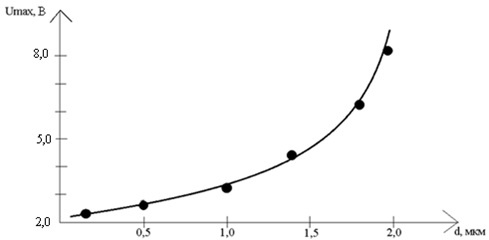

В результате была получена зависимость максимального напряжения питания, являющегося критическим фактором в отношении перехода схем в режим защелки, от параметров, характеризующих типовые размеры элементов схем (рис. 3). Видно, что по мере совершенствования схем, величина критического напряжения питания уменьшается.

Рис. 3. График зависимости максимального напряжения питания от ширины металлизации.

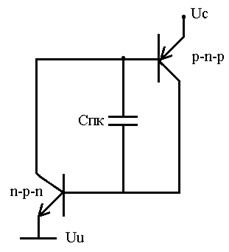

Восприимчивость к эффекту «защелкивания» исследовали на КМОП схемах с n-карманами. Известно, что в КМОП схемах, которые питаются от источника постоянного тока, между подложкой и карманом образуется обедненная область. Основные носители (электроны для n-кармана и дырки для р- кармана) движутся к соответствующим контактам, что приводит к падению напряжения и тем самым – смещению р-n перехода. При достаточном прямом напряжении смещения возникает «защелкивание». Эквивалентные схемы использованных КМОП схем приведены на рис. 4- 6. Они соответствуют схемам, в которых карман находится под плавающим потенциалом обратносмещенной подложки (рис. 4), стандартной логической схемы с заземленной р- подложкой и n-карманом, подсоединенным к положительному источнику напряжения (рис. 5), и логической схемы с генератором напряжения положительного смещения на подложке и n-карманом, подсоединенным к источнику положительного напряжения (рис. 6).

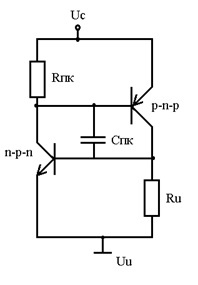

Рис.4. Схема, в которых карман находится под плавающим потенциалом обратносмещенной подложки.

Схема на рис. 4 состоит из вертикального и горизонтального паразитного биполярных транзисторов и емкости подложка - карман Cпк. Определяющими защелкивание параметров является заряд базы р-n-р транзистора одного из биполярных транзисторов и зарядом обусловленный емкостью Cпк. Любое изменение соотношения этих зарядов критично при различных концепциях масштабирования.

Рис.5. Схема с заземленной р- подложкой и n-карманом, подсоединенным к положительному источнику напряжения.

Для стандартных логических КМОП ИС (рис. 5) важными параметрами являются Rи, Rпк и Cпк. При всех концепциях масштабирования сопротивления в первом приближении можно считать постоянными.

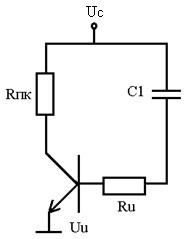

Рис. 6. Схема с напряжением положительного смещения на подложке и n-карманом, подсоединенным к источнику положительного напряжения.

Для схемы на рис. 6 наиболее важными параметрами является коэффициент усиления по току горизонтального транзистора n-р-n транзистора и емкость С1. Опасность возникновения защелкивания снижена только для стандартных логических схем, а все схемы, имеющие источник напряжения смещена на подложке, особенно динамические ПЗУ, весьма, подвержены защелкиванию. В таких случаях необходимо предусматривать схемы защиты, которые ограничивают скорость роста напряжения внутри прибора [9]. Применение сильнолегированной подложки с эпитаксиальным слоем не решает задачу борьбы с защелкиванием данного вида, поскольку из-за более высокого коэффициента усиления по току горизонтального биполярного транзистора такие схемы вдвое более чувствительны к защелкиванию, чем схемы на объемного кремнии.

КМОП схемы рассмотренных вариантов исследовали на подверженность эффекту защелкивания, обусловленного воздействием импульсов (например, положительным или отрицательным выбросом на фронте импульса, сбоями), которая связана не только с уменьшением заряда базы р-n-р транзистор, но и снижением длительности переходных процессов в базе паразитных биполярных транзисторов. Защелкивание могут вызвать даже кратковременные (менее 1 нс) сбои. В качестве методов предотвращения защелкивания данного типа предлагаются следующие: использование диодов с барьером Шоттки или специальных поликремниевых р+- n+ - диодов вместо омических контактов подложки и кармана; применение сильнолегированной подложки с изоляцией щелевидными канавками, которые распространяются на большую глубину в область с высоким уровнем легирования.

Следует также отметить, что представленные результаты справедливы и для структур с р-карманами, так как механизмы, вызывающие появления защелкивания, не зависит от типа проводимости области кармана.

Библиография

1. Farbiz F., Rosenbaum E. Modeling and Understanding of External Latchup in CMOS Technologies—Part I: Modeling Latchup Trigger Current //IEEE Transactions on Device and Materials Reliability, vol. 11, no. 3, pp. 417-425, Sept. 2011.

2. Мустафаев Г.А., Мустафаев А.Г., Мустафаев А.Г. Влияние конструкции на характеристики субмикронных КНИ МОП-транзисторов // Нано и микросистемная техника. 2010. № 7. С. 8-12.

3. Karp J., M. Hart J., Maillard P., Hellings G., Linten D. Single-Event Latch-Up: Increased Sensitivity From Planar to FinFET // IEEE Transactions on Nuclear Science, vol. 65, no. 1, pp. 217-222, Jan. 2018.

4. Kontos D., Domanski K., Gauthier R. et al. Investigation of external latchup robustness of dual and triple well designs in 65nm bulk cmos technology // Proc. of the International Reliability Physics Symposium, 2006. pp. 145–150.

5. Мустафаев Г.А., Мустафаев А.Г., Черкесова Н.В. Надежность интегральных микросхем с алюминиевой металлизацией//Электроника и электротехника. 2017. № 3. С.1-6.

6. Voldman S., Gebreselasie E., Zjerak M. et al. Latchup in merged triple well structure // IEEE International Reliability Physics Symposium, 2005. pp. 129–136.

7. Tsai H., Ker M. Compensation circuit with additional junction sensor to enhance latchup immunity for CMOS integrated circuits // 2015 European Conference on Circuit Theory and Design (ECCTD), Trondheim, 2015, pp. 1-4.

8. Muth W. Matrix method for latch-up free demonstration in a triple-well bulk-silicon technology // IEEE Transactions on Nuclear Science, 1992. Vol. 39. № 3. pp. 396–400.

9. Li Y., Gong X., Xu W., Hong Z., Killat D. An experimental extracted model for latchup analysis in CMOS process // 2009 IEEE 8th International Conference on ASIC, Changsha, Hunan, 2009, pp. 1035-1038.

References

1. Farbiz F., Rosenbaum E. Modeling and Understanding of External Latchup in CMOS Technologies—Part I: Modeling Latchup Trigger Current //IEEE Transactions on Device and Materials Reliability, vol. 11, no. 3, pp. 417-425, Sept. 2011.

2. Mustafaev G.A., Mustafaev A.G., Mustafaev A.G. Vliyanie konstruktsii na kharakteristiki submikronnykh KNI MOP-tranzistorov // Nano i mikrosistemnaya tekhnika. 2010. № 7. S. 8-12.

3. Karp J., M. Hart J., Maillard P., Hellings G., Linten D. Single-Event Latch-Up: Increased Sensitivity From Planar to FinFET // IEEE Transactions on Nuclear Science, vol. 65, no. 1, pp. 217-222, Jan. 2018.

4. Kontos D., Domanski K., Gauthier R. et al. Investigation of external latchup robustness of dual and triple well designs in 65nm bulk cmos technology // Proc. of the International Reliability Physics Symposium, 2006. pp. 145–150.

5. Mustafaev G.A., Mustafaev A.G., Cherkesova N.V. Nadezhnost' integral'nykh mikroskhem s alyuminievoi metallizatsiei//Elektronika i elektrotekhnika. 2017. № 3. S.1-6.

6. Voldman S., Gebreselasie E., Zjerak M. et al. Latchup in merged triple well structure // IEEE International Reliability Physics Symposium, 2005. pp. 129–136.

7. Tsai H., Ker M. Compensation circuit with additional junction sensor to enhance latchup immunity for CMOS integrated circuits // 2015 European Conference on Circuit Theory and Design (ECCTD), Trondheim, 2015, pp. 1-4.

8. Muth W. Matrix method for latch-up free demonstration in a triple-well bulk-silicon technology // IEEE Transactions on Nuclear Science, 1992. Vol. 39. № 3. pp. 396–400.

9. Li Y., Gong X., Xu W., Hong Z., Killat D. An experimental extracted model for latchup analysis in CMOS process // 2009 IEEE 8th International Conference on ASIC, Changsha, Hunan, 2009, pp. 1035-1038.

|

Статья опубликована с лицензией Creative Commons Attribution-NonCommercial 4.0 International License (CC BY-NC 4.0) – Лицензия «С указанием авторства – Некоммерческая».

Статья опубликована с лицензией Creative Commons Attribution-NonCommercial 4.0 International License (CC BY-NC 4.0) – Лицензия «С указанием авторства – Некоммерческая».

Рус

Рус